Vivado has the ability to create and manage your own IP, which is a good thing. But there are some real gotchas when doing something like this, the first being that it doesn’t seem to place HDL files in the correct locations.

I have been running some FPGA workshops using the IP Packager in Vivado and having been having a lot of problems when creating new files in the IP component. Here’s an example:

From a Vivado project select Tools→Create and Package IP… Click Next, select Create a new AXI4 peripheral, click Next, just use the defaults for the next page, click Next again, use the defaults for the AXI information and click Next again, select Edit IP, then click Finish.

This will put in an IP Packager project. Edit the top level file myip_v1_0. I’m using Verilog but it works the same for VHDL. Instantiate a new dummy module at the bottom of the file:

// Add user logic here dummy dummy (.clk(s00_axi_aclk)); // User logic ends

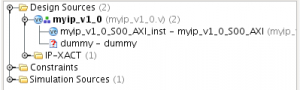

Save the file and look at the design sources. You will see that there is now a new undefined module in the design called dummy. It should look like the figure to the right:

Save the file and look at the design sources. You will see that there is now a new undefined module in the design called dummy. It should look like the figure to the right:

Now, we would like to create the new module. So we go to File→Add Sources… and create the new source file. Select Add or create design sources and click Next. Click Create File …, type the file name dummy and click OK. Click Finish. When the Define Module dialog pops up, just click OK. Click Yes to the dialog saying you haven’t changed anything. You now have a file defined for your dummy module.

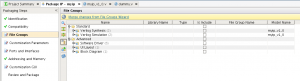

Ready to package that IP? Go to the Package IP tab in the Project Manager window. Then, select File Groups in the Packaging Steps window. You should see a window like the figure on the right.

Ready to package that IP? Go to the Package IP tab in the Project Manager window. Then, select File Groups in the Packaging Steps window. You should see a window like the figure on the right.

Now click on the Merge changes from File Groups Wizard link. You will then get a link saying 2 warnings. Click on that, and you will see two warnings about your dummy.v file being on a path which is not relative to your IP root directory. What has happened is that Vivado placed the new file outside the IP component. If you go ahead and package your IP, you cannot use the packaged IP because it will be missing this file. Seems like a Vivado (2014.4) bug to me.

So how should we fix this? I don’t know how to move files in Vivado, but we can create the file in a different location when we make the new file. To do that, first delete the dummy file and remove it from disk. Just select the file, then right-click and select Remove File from Project. Select the checkbox to also delete it from disk and click OK.

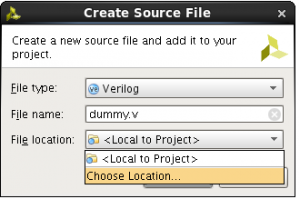

Now go to Add Sources again, and after clicking Create File…, specify the file name dummy.v, then select a new file location.

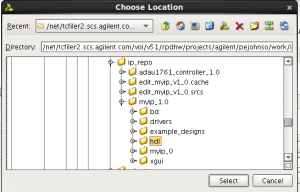

Now go to Add Sources again, and after clicking Create File…, specify the file name dummy.v, then select a new file location.  Navigate to your ip_repo area and into myip_1_0. Select the hdl directory, and click Select. Then click OK and then Finish to create the file. This will place the file in the proper location in the IP repository.

Navigate to your ip_repo area and into myip_1_0. Select the hdl directory, and click Select. Then click OK and then Finish to create the file. This will place the file in the proper location in the IP repository.

When you merge your changes in the File Groups step, you should not get any warnings. You can then package your IP and use it in your designs.

Hopefully this will be fixed in the next release of Vivado.

thanx for the workaround

So would you delete files you have worked on for hours and hours only to find POS Vivado gives the warning when you try to wrap things up?

Im being rhetorical. Your solution is not good.

Also note files can get deleted when this warning exists. Yes, deleted if you close out of the ‘packager’.

Im using 15.4.2 and the issue remains. As do soooooooooooooooooo many in Vivado.

It’s just a very unstable, buggy, intern written tool.

1. For the files giving warnings, note their locations via Vivado’s property window. Basically click on the file and look at the property window to find the files present location.

2. Don’t delete the files, merely remove them from the Packager project.

3. Note the location of a file initially created by the packager when you got through the

‘add/create files’ wizard. That location is where Vivado wants your ‘created after the fact’ files.

4. Move your warning files to the location in 3 and ‘remerge’ the files in the packager and the warnings will be gone.

This works for design files but my guess is it will work for sim files etc as well.

Just a terrible, frustrating tool.

Yes, Vivado has a lot of problems. It can be very frustrating to use. I am particularly bothered by its lack of scripting support. And by scripting support I don’t mean running TCL scripts. I mean running Vivado from the command line. It is basically impossible. And you can’t use it for block designs without using the project flow. But in many important ways it is an improvement over ISE. In all though, I think Quartus II is a much better thought out tool for more advanced users.

Right on Pete: Here’s a reply from my buddy who works on MPSoC at Xilinx after I ranted to him about the awful Vivado about 3 months ago:

——————————————————————————————

“I will add your concerns to the GIANT FUCKING MOUNTAIN of them already outside the building. But they recently fired the person who was reading all the hate mail, so you’re comments might have to wait a while before they are read 😉

Try sticking to a *.4 version. They tend to be most stable and have all the bug fixes for the year”

——————————————————————————————

Apologies for the straight forward language, but there you go. From the horses mouth.

Just an awful, buggy tool.

PS I found this page again because Im having the same issue in 16.1 LOL!

I hadn’t realized the releases worked that way. And I just installed 2016.1. I guess I will have to be on the lookout for bad behavior.

Thanks a lot for the solution.. It certainly helped 🙂

Hi pete,

I want to do like in one register store a value and send it to arm.how to do this?I am using zynq zc702 fpga.

Hi pete,

I want to do like in one register store a value and send it to arm.how to do this?I am using zynq zc702 fpga.

Thanks mate!!